Multi-Feature and Balanced Search Tree Based Depth Range Definition in HEVC Inter Prediction for VLSI Implementation

Abstract

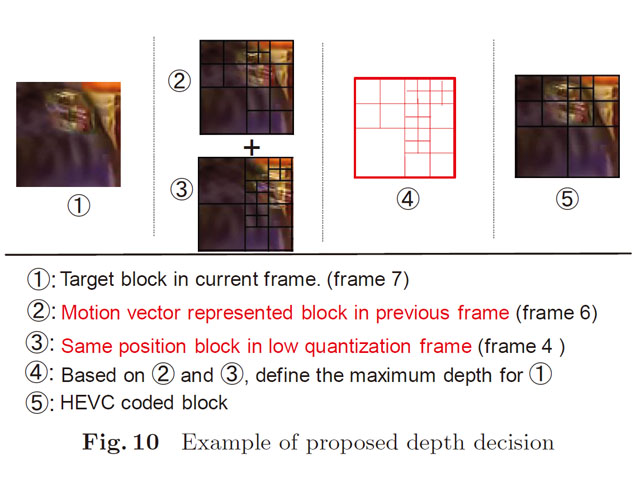

High efficiency video coding (HEVC) is a video compression standard that outperforms the predecessor H.264/AVC by almost doubling the compression performance. To enhance the compression performance, the partition sizes is ranging from 4 × 4 to 64 × 64 in HEVC. However, the manifold partition sizes dramatically increase the encoding complexity. A lot of works focused on reducing the complexity but didn’t consider the feasibility of hardware implementation. This paper proposes a hardware friendly fast depth decision algorithm based on multiple features and balanced search tree. The minimum partition size is defined by multiple features, including quantization, texture and motion features. The balanced search tree will further define the depth search range. Our algorithm is VLSI friendly since the longest path of depth decision processing is reduced from four to three. Experimental results show that the proposed method saves about 32.18 % of the original processing time with 0.79 % of BD-bitrate increase on average. Keywords: HEVC, inter prediction, block texture, quantization, motion, depth decision

Author

Gaoxing CHEN*, Zhenyu LIU**, Tetsunori KOBAYASHI***, Takeshi IKENAGA*

*Graduate School of Informaton, Production and Systems, Waseda University , **TNList, Tsinghua University , ***Faculty of Science and Engineering, Waseda University