FPGA Accelerator for Super-pixel Segmentation Featuring Clear Detail and Short Boundary

あらまし

Super-pixel segmentation is to over-divide an image to get object boundaries. This is positioned as preprocessing for advanced image processing such as image division and object recognition.

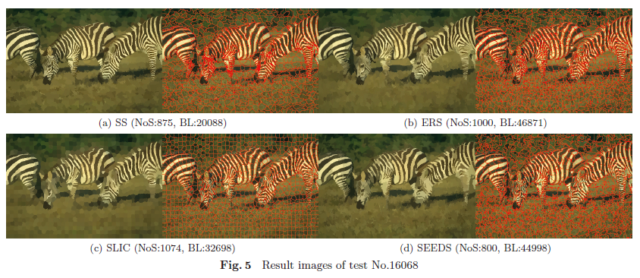

This paper proposes a novel fast and accurate super-pixel segmentation algorithm. The proposed method starts from the initial division of a regular grid and hierarchically repeats boundary update using an energy function in local. The energy function consists of a penalty term and a regularization term. The penalty term expresses the color similarity between a pixel and a super-pixel. The regularization term expresses the spatial continuity of the super-pixel. Experimental results show that the proposed method is two to ten times faster than the conventional methods and there is no significant decrease in accuracy. The accuracy against the boundary length is overwhelmingly higher in particular. The object inside is meaningfully divided and the detail of the object is clear in the image where each pixel is replaced with the average of the super-pixel. Furthermore, a dedicated processor based on this algorithm was designed. By adopting a line buffer, a region table of 16 banks, forwarding of the left result, and a cache for updating region data, the processor free from pipeline stall achieves throughput of 1 pixel / 1 cycle. The throughput of the processor implemented on an FPGA was VGA 42.2 fps when operating at 30 MHz. This was five times faster than a software implementation running on a PC at 3 GHz.

著者

Masayuki MIYAMA† (Member)

† Faculty of Electrical and Computer Engineering, Institute of Science and Engineering, Kanazawa University